В опубликованной 21 октября 2020 года на портале CNews статье1 говорится о том, что государство будет поддерживать разработку и серийное производство «микропроцессоров для бортовых систем управления, программно-совместимых с микропроцессорами 1890ВМ6Я и 1890ВМ7Я». Кто займется разработкой таких устройств — пока не понятно, объявлен тендер. Но нас, в первую очередь, интересует технологичность аппаратуры, которая будет создаваться на основе таких микросхем, в частности — её тестопригодность. Ну и, конечно, стоимость тестирования, которая напрямую зависит от тестопригодности.

1890ВМ6Я и 1890ВМ7Я — это линейка процессоров «КОМДИВ», развитием архитектуры которой занимается НИИ системных исследований Российской академии наук (НИИСИ РАН). Когда речь заходит о тестопригодности цифровых плат, то первым наиболее применимым в этом случае тестовым методом является периферийное сканирование. У разработок НИИСИ РАН стандарт периферийного сканирования (IEEE 1149.1) поддерживается очень широко, что не может не вселять надежду на применение средств автоматизированного электроконтроля. В списке микросхем, разработанных НИИСИ, есть 38 позиций, поддерживающих периферийное сканирование. Это говорит о том, что данная технология давно и досконально известна сотрудникам института. По нашим данным, это — максимальная номенклатура с поддержкой стандарта IEEE 1149.1 среди продуктовых линеек отечественных разработчиков ЭКБ.

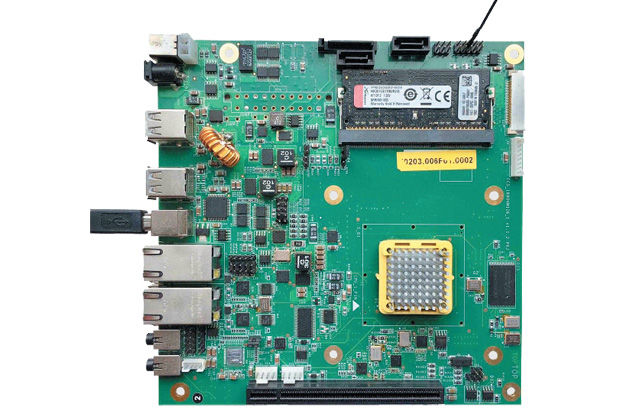

Не так давно к нам попала отладочная плата для системы-на-кристалле 1890ВМ128 (рис 1), это произошло еще до публикации новости о поддержке процессоров НИИСИ. По иронии судьбы два этих события совпали. 1890ВМ128 представляет собой высокопроизводительный графический процессор на кристалле с

Для проверки работы периферийного сканирования мы использовали программный пакет JTAG ProVision, в котором на основе предоставленного нетлиста исследовательской платы (файла списка цепей из САПР) был создан проект и сгенерированы приложения для тестирования. Контроллер периферийного сканирования в данном случае не понадобился, так как канал сканирования на тестируемой плате всего один, а в ее схеме присутствует микросхема FTDI FT2232, преобразующая JTAG-интерфейс в USB.

Давайте разберем, что же удалось проверить.

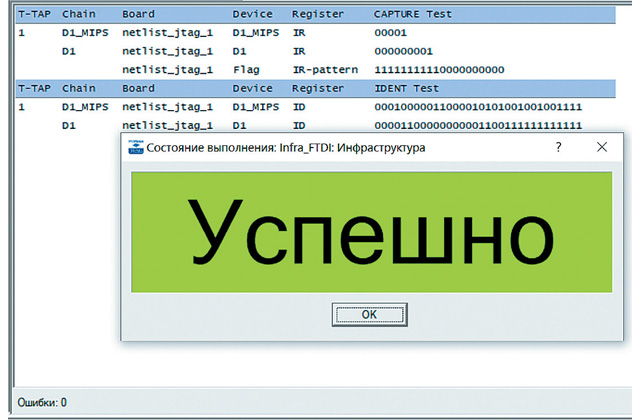

Тест инфраструктуры

Это стандартный тест для всех компонентов с поддержкой JTAG, он генерируется в JTAG ProVision автоматически и проверяет работу регистра команд и

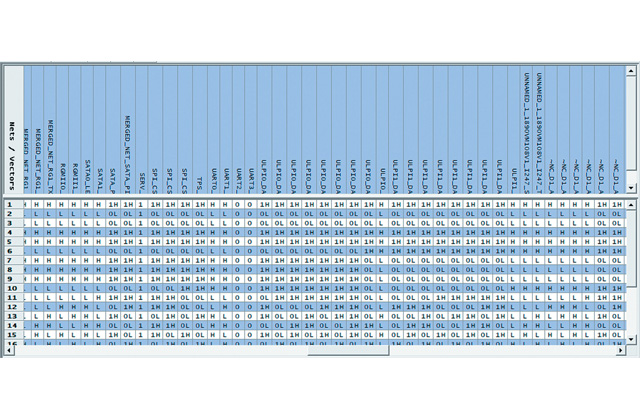

Тест межсоединений

Как правило, тест межсоединений — это самый объемный тест периферийного сканирования. Он генерируется автоматически и «прозванивает» все цепи печатного узла, к которым есть доступ периферийного сканирования. В зависимости от конфигурации цепи и количества компонентов с поддержкой JTAG с помощью этого приложения можно обнаруживать обрывы (непропаи), замыкания, перепутывания проводников. Полностью успешно тест межсоединений прошел после корректировки BSDL-файла в части описания выводов микросхемы. Как эти неточности были обнаружены и исправлены — это тема отдельной статьи. По итоговой таблице векторов (рис 3) видно, что установка и считывание тестовых битов микросхемой 1890ВМ128 происходит корректно.

На исследовательской плате присутствует разъем soDIMM, и при использовании в системе периферийного сканирования модуля тестирования

Таблица 1 Состояние поддержки периферийного сканирования российской ЭКБ

|

№№ |

Предприятие-разработчик ЭКБ |

Заявленное наличие компонентов с поддержкой стандартов IEEE 1149.x |

Есть данные о корректной работе периферийного сканирования |

|

1 |

Байкал Электроникс |

Нет |

Нет |

|

2 |

ВЗПП-С |

Да |

Да |

|

3 |

МЦСТ |

Да |

Да |

|

4 |

НИИИС им. Седакова |

Да |

Да |

|

5 |

НИИСИ РАН |

Да |

Да |

|

6 |

НИИЭТ |

Да |

Да |

|

7 |

НПП «Цифровые Решения» |

Да |

Да |

|

8 |

НТЦ Модуль |

Да |

Да |

|

9 |

ПКК Миландр |

Да |

Да |

|

10 |

ЭЛВИС |

Да |

Нет |

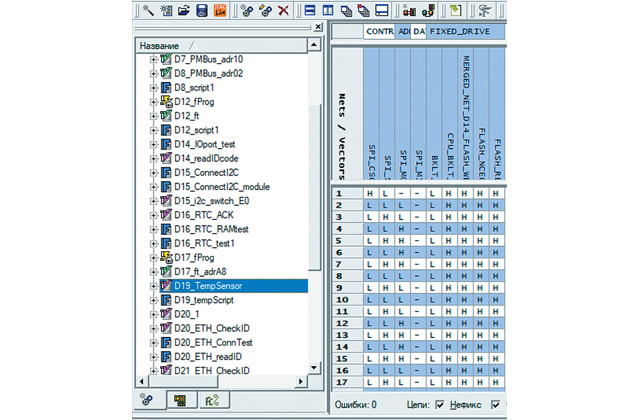

Тестирование кластеров исследовательской платы

С помощью регистра периферийного сканирования микросхемы 1890ВМ128 удалось протестировать целый набор окружающих кластеров (то есть микросхем, не поддерживающих периферийное сканирование). Автоматически получилось сгенерировать и запустить тесты регуляторов напряжения по интерфейсу SPI, тест флэш-памяти с последовательным интерфейсом, а также приложение для ее программирования. По готовым моделям периферии из библиотеки JTAG ProVision cделаны и выполнены тесты контроллера Ethernet, температурного датчика и часов реального времени. А с помощью дополнительного инструмента JTAG Functional Test удалось протестировать функции вышеуказанных кластеров более глубоко, например, измерить температуру, проверить изменение времени и даты в RTC, проверить работу I2C-мультиплексора. Неполный список тестов приведен на рис 4.

Выводы

Необходимо отметить, что все вышеперечисленные тесты выполнены с помощью регистра периферийного сканирования без необходимости создавать какое-либо тестовое ПО, которое нужно загружать в плату. Не нужно интерпретировать результаты некорректного прохождения тестов из этого ПО или, например, оперативно его изменять. В этом преимущество технологии периферийного сканирования — независимость разработчика и производственных площадок друг от друга. Старый вариант, когда все держат друг друга на поводке, уже не работает в сегодняшнем мире.

Так как функциональный тест не диагностирует дефекты монтажа до уровня пинов микросхем, а его интерпретацией могут заниматься только специалисты, разработавшие изделие, то часто не проходящие проверку платы отправляются в брак. Это работает до момента, когда стоимость брака не превышает критических величин. Затем принимаются меры по исправлению брака, и за неимением средств автоматизированного структурного контроля эти меры выливаются в наем специалистов и покупку излишнего оборудования, да и логистика усложняется.

Производить платы на базе процессоров КОМДИВ — дешевле. Потому что есть периферийное сканирование. При этом стандарт IEEE 1149.1 открыт, его применение на кристалле ничего не стоит: ни лишних денег, ни места в топологии. Если касаться времени создания тестов, то здесь функциональный тест тоже проигрывает. ПО для тестирования создается несколько месяцев (при наличии хороших программистов), при том, что для диагностики оно чаще всего бесполезно, а тесты периферийного сканирования генерируются в течение нескольких часов (можно добавить пару дней на отладку и «обкатку»). Поэтому хорошо, если российские разработчики получат процессоры именно с архитектурой КОМДИВ, и тут главное, чтобы конечный разработчик ничего не упустил и не забыл поставить галочку в САПР микроэлектроники для вставки периферийного сканирования!

А что же с остальными российскими разработками? В Таблице 1 приведен список отечественных разработчиков цифровой ЭКБ, составленный по нашему исследованию2. В нем проектировщик схемы может увидеть, использование цифровых чипов каких разработчиков удешевит и упростит весь жизненный цикл будущей аппаратуры.

1 https://www.cnews.ru/news/top/2020-10-20_vlasti_rossii_potratyat_270

2 Иванов А. Современное состояние поддержки периферийного сканирования отечественной электронной компонентной базой // ЭЛЕКТРОНИКА: Наука, Технология, Бизнес. 2020. № 6. С.